前回はメモリのセルの内部構造とそれがどうやって 1 ビットを表現しているかを見てきました。今回は範囲を広げ、CPU が DRAM(メモリ)をどう動かしているかに焦点をあてていきます。

Indexx

メモリコントローラ とは

メモリコントローラは CPU の中に組み込まれている LSI(大規模な IC のこと。Large Scale Integration、大規模集積回路)で、メモリの制御やメモリに保存されているデータを読み取って他の IC に送信する役割を持っています。

IC の規模の種類

IC は含まれているトランジスタやキャパシタなどの素子の数によりいくつかの種類に分けられます。

- SSI:小規模集積回路。数十個のトランジスタを含む回路。

- MSI : 中規模集積回路。数百から数千のトランジスタを含む回路。

- LSI : 大規模集積回路。数千から数百万のトランジスタを含む回路。メモリコントローラはこの規模に該当する。

- VLSI : 超大規模集積回路。数百万から数十億のトランジスタを含む回路。

- ULSI :最も高度な超大規模集積回路。VLSI以上の規模で、数十億以上のトランジスタを含む。

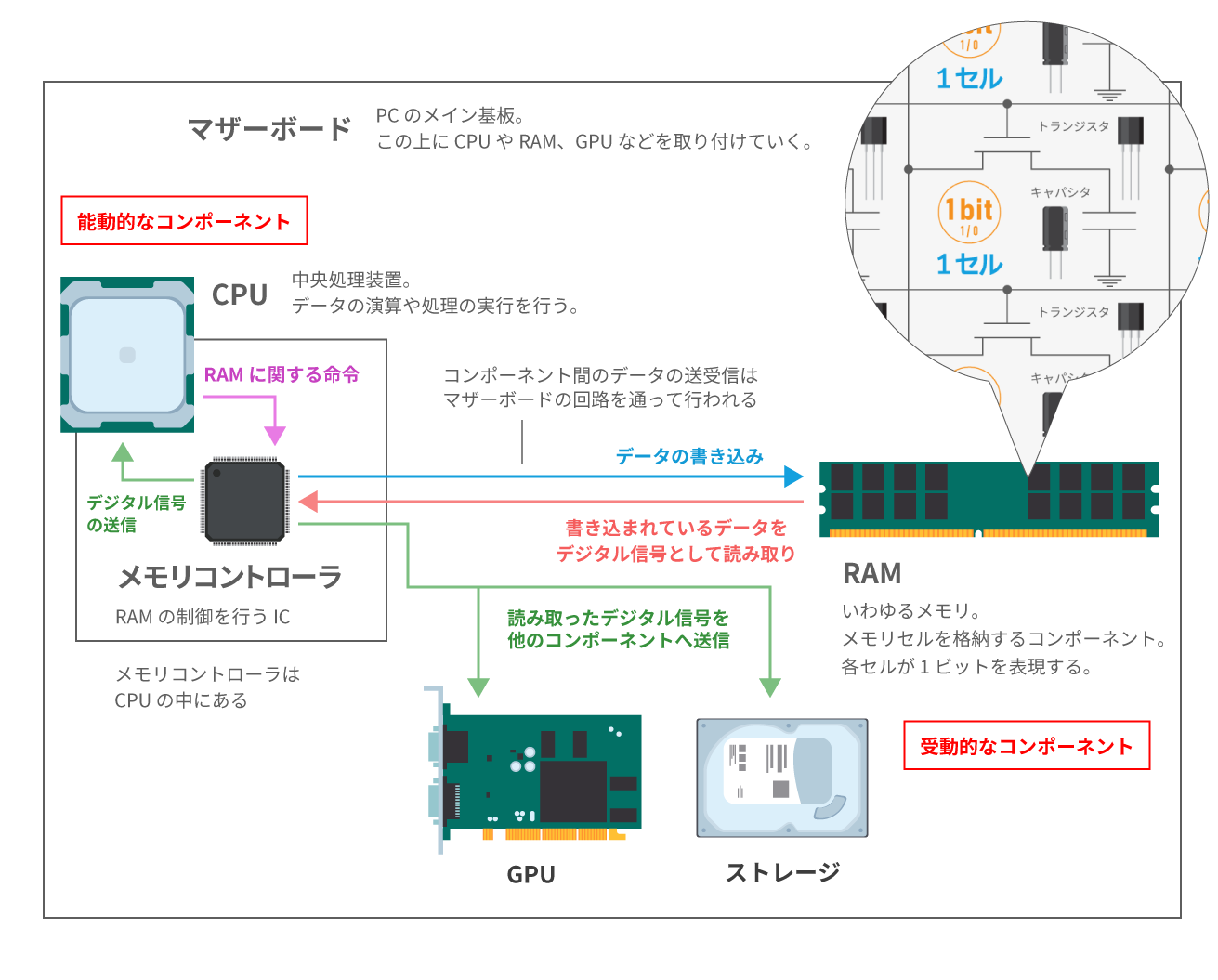

各コンポーネントとの関係性

メモリコントローラを格納している CPU や RAM はマザーボード上に配置され、メモリコントローラ / RAM 間の通信はマザーボード上の回路と IC が担います。

CPU はあらゆる指令を出すコンポーネントなので能動的なコンポーネントです。

それに対しその他のコンポーネントは CPU からの指令を受けて処理を行うため、受動的なコンポーネントと言えます。RAM もまた自身でデータを読み書きするのではなく、CPU にあるメモリコントローラからの指示で処理を行います。

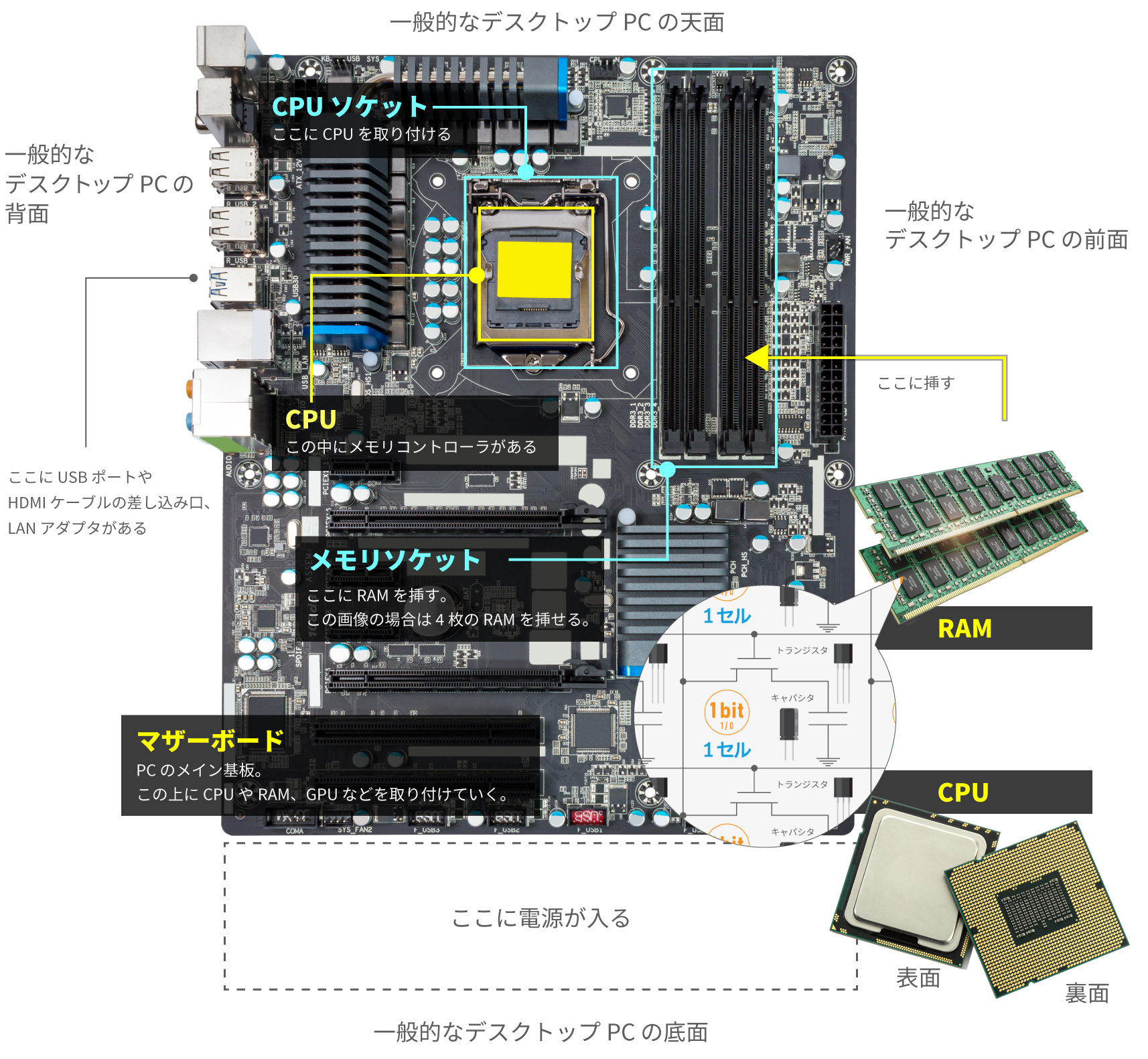

位置関係

下記は実際の画像で見るマザーボード / CPU / RAM の位置関係です。

フリー素材なのでマザーボードなどの型番は不明です。

RAM へのデータの読み書き

今回は特定のセルに対してメモリコントローラがどうやってデータの読み書きを行っているかについて見ていきます。具体的には

メモリコントローラを基準にした構図は下記のようになっています。

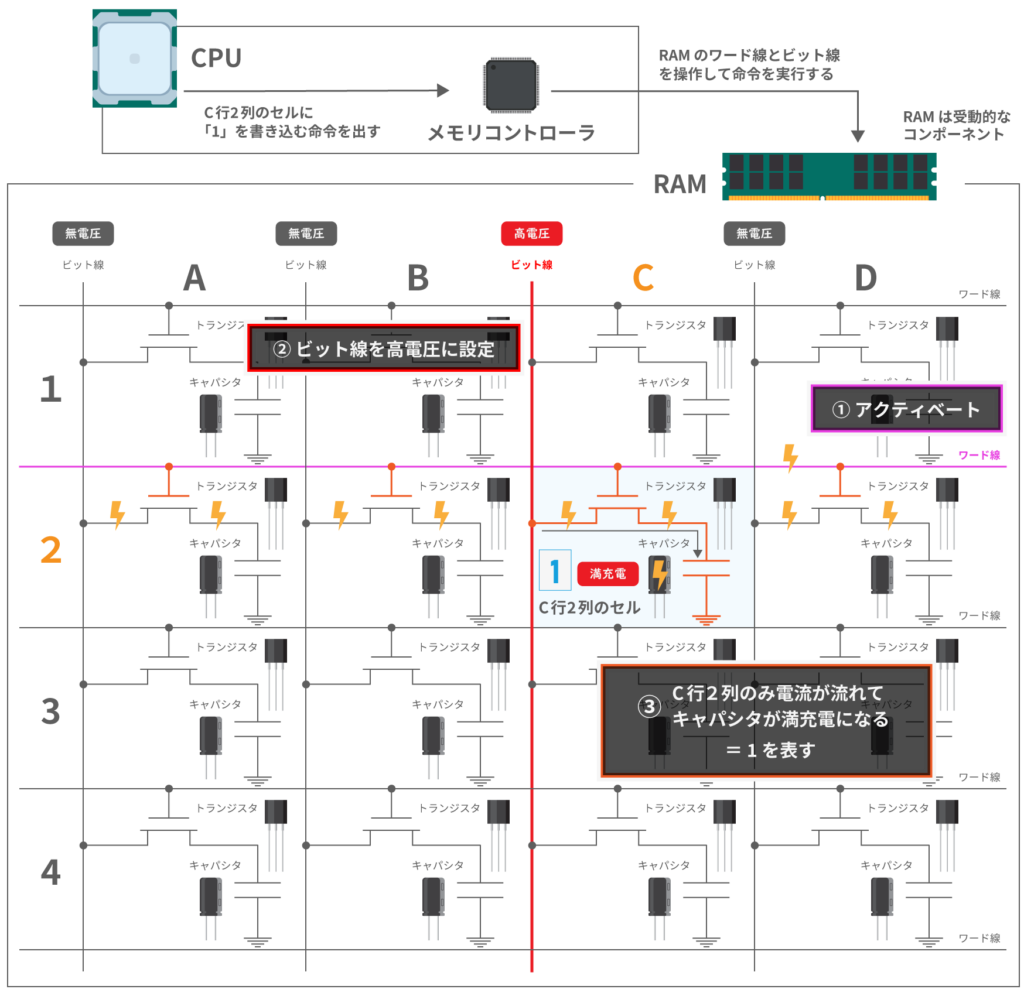

アクティベーション

データの書き込み / 読み取りはすべてアクティベーションから始まります。前回やったように、アクティベーションはワード線に電流を流してトランジスタを ON にすることです。

アクティベーションの段階では電流は流れない

アクティベートを行った段階では電流は流れません。

そのため、キャパシタに電荷がある状態(つまり「1」を指している状態)であったとしても、そのキャパシタが放電されて電荷が減少することはありません。

放電されるのはビット線をグラウンドに繋いで低電圧にした場合です。

「1」を書き込む

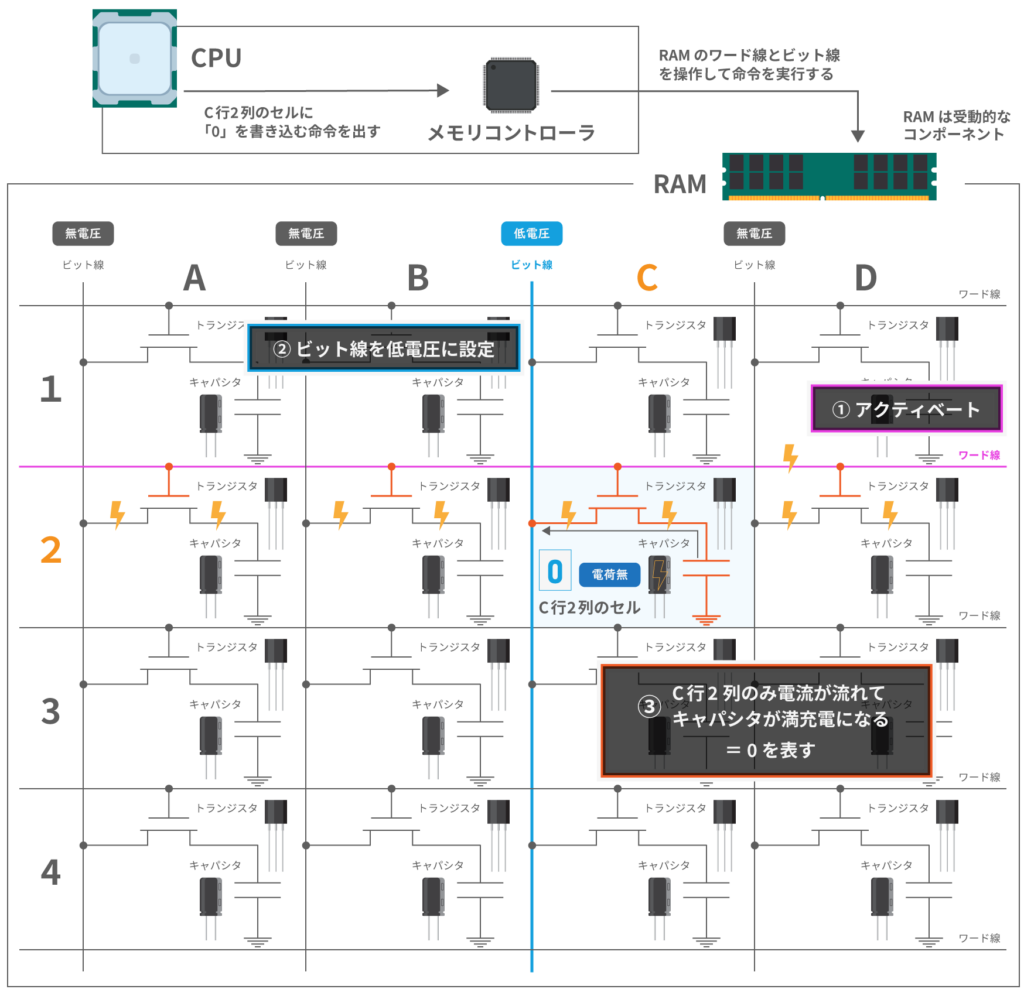

「0」を書き込む

データの読み取り

「o」と「1」の違いは電流の向きの違いだけです。

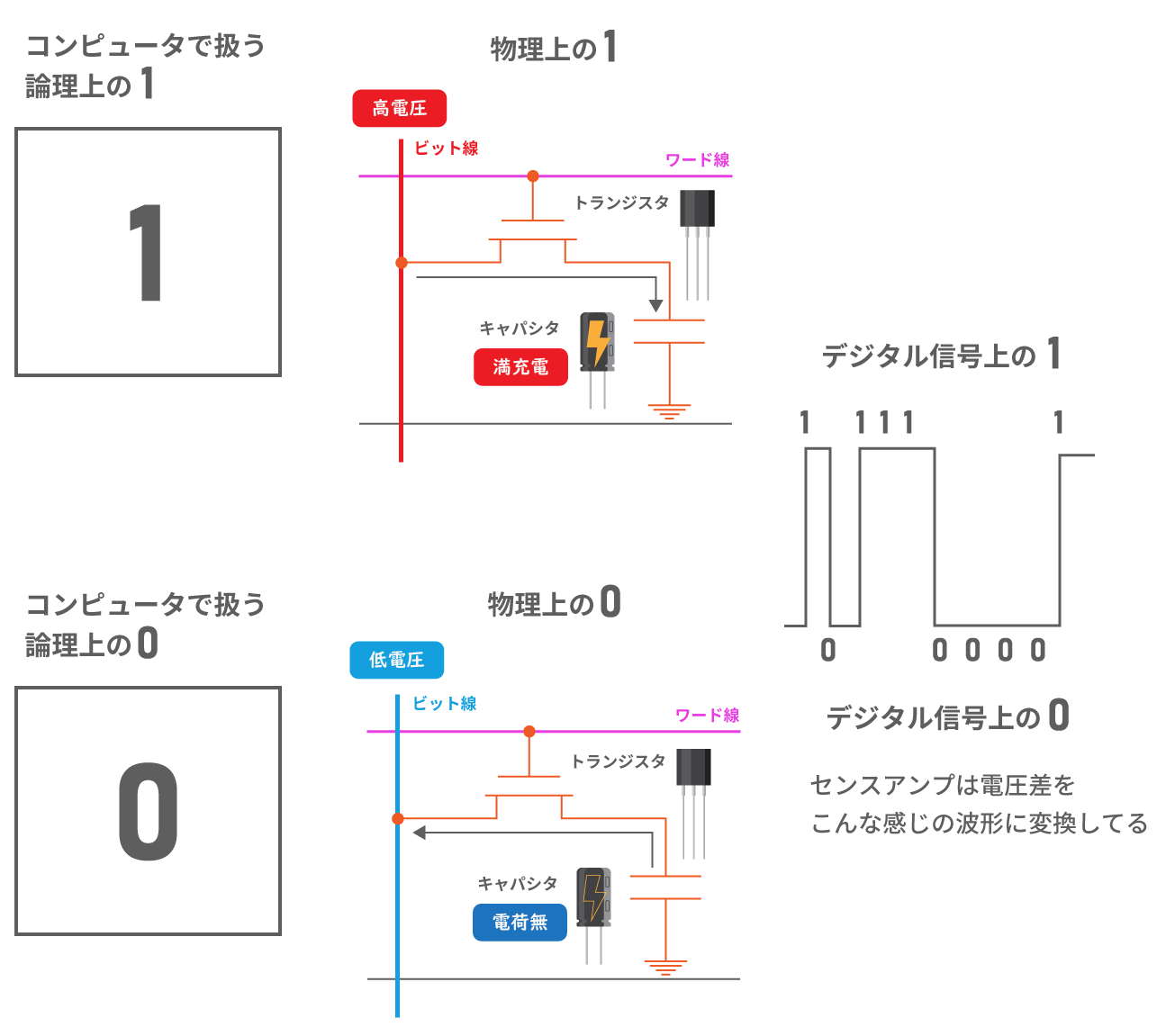

まとめ:論理と物理

論理上の 0 や 1 と物理上の「0」や「1」は違います。

コンピュータは上記のようにトランジスタとキャパシタを使用して 1 や 0 を表現していて、それらはメモリコントローラが RAM のワード線とビット線を制御して行います。メモリが表現する 0 / 1 はデジタル信号の値です。

前回と今回は DRAM 上で 1 ビットをどう読み書きするかについて扱ってきました。次回は数バイト以上の単位をコンピュータがどう扱っているかを見ていきます。まだメモリの話が続きます。

LEAVE A REPLY